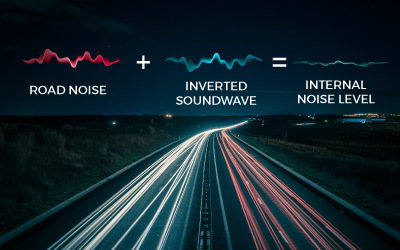

Figure 1. Noise cancelation principle

Figure 2. Active road noise cancelation system block diagram

The implementation of the HIL system for active noise cancelation in the car was performed in the VHDL hardware description language. Synthesis and implementation were done in Xilinx Vivado Design Suite. The FPGA part of the system was implemented on Xilinx Virtex UltraScale+ development board. ADC and DAC were mounted on separated boards connected with a FMC connector with the FPGA development board. The main challenge was to achieve fixed audio latency from input (ADC) to output (DAC). Linux operating system was used for that purpose.

Conclusion

The project covered the complete development, from the system architecture planning, to ADC/DAC extension board development, to RTL design and verification, to driver development and complete product integration. All the development steps were conducted by RT-RK.

HIL device analog board

HIL device interior